从电源系统的角度进行去耦设计

四、从电源系统的角度进行去耦设计

这一节就来讲讲另一种方法,从电源系统的角度进行去耦设计。该方法本着这样一个原则:在感兴趣的频率范围内,使整个电源分配系统阻抗 低。其方法仍然是使用去耦电容。

电源去耦涉及到很多问题:总的电容量多大才能满足要求?如何确定这个值?选择那些电容值?放多少个电容?选什么材质的电容?电容如何安

四、从电源系统的角度进行去耦设计

这一节就来讲讲另一种方法,从电源系统的角度进行去耦设计。该方法本着这样一个原则:在感兴趣的频率范围内,使整个电源分配系统阻抗 低。其方法仍然是使用去耦电容。

电源去耦涉及到很多问题:总的电容量多大才能满足要求?如何确定这个值?选择那些电容值?放多少个电容?选什么材质的电容?电容如何安装到电路板上?电容放置距离有什么要求?下面分别介绍。

1、目标阻抗

目标阻抗(Target Impedance)定义为:

该定义可解释为:能满足负载 大瞬态电流供应,且电压变化不超过 大容许波动范围的情况下,电源系统自身阻抗的 大值。超过这一阻抗值,电源波动将超过容许范围。如果你对阻抗和电压波动的关系不清楚的话,请回顾“电容退耦的两种解释”一节。

对目标阻抗有两点需要说明:

1、目标阻抗是电源系统的瞬态阻抗,是对快速变化的电流表现出来的一种阻抗特性。

2、目标阻抗和一定宽度的频段有关。在感兴趣的整个频率范围内,电源阻抗都不能超过这个值。阻抗是电阻、电感和电容共同作用的结果,因此必然与频率有关。感兴趣的整个频率范围有多大?这和负载对瞬态电流的要求有关。顾名思义,瞬态电流是指在极短时间内电源必须提供的电流。如果把这个电流看做信号的话,相当于一个阶跃信号,具有很宽的频谱,这一频谱范围就是我们感兴趣的频率范围。

如果暂时不理解上述两点,没关系,继续看完本文后面的部分,你就明白了。

2、需要多大电容量

有两种方法确定所需的电容量。 种方法利用电源驱动的负载计算电容量。这种方法没有考虑 ESL 及 ESR 的影响,因此很不 确,但是对理解电容量的选择有好处。第二种方法就是利用目标阻抗(Target Impedance)来计算总电容量,这是业界通用的方法,得到了广泛验证。你可以先用这种方法来计算,然后做局部微调,能达到很好的效果,如何进行局部微调,是一个更 的话题。下面分别介绍两种方法。

方法一:利用电源驱动的负载计算电容量

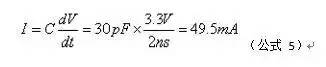

设负载(容性)为 30pF,要在 2ns 内从 0V 驱动到 3.3V,瞬态电流为:

如果共有 36 个这样的负载需要驱动,则瞬态电流为:36*49.5mA=1.782A。假设容许电压波动为:3.3*2.5%=82.5 mV,所需电容量为C=I*dt/dv=1.782A*2ns/0.0825V=43.2nF

说明:所加的电容实际上作为抑制电压波纹的储能元件,该电容必须在2ns 内为负载提供1.782A 的电流,同时电压下降不能超过 82.5 mV,因此电容值应根据 82.5 mV 来计算。记住:电容放电给负载提供电流,其本身电压也会下降,但是电压下降的量不能超过 82.5mV(容许的电压波纹)。这种计算没什么实际意义,之所以放在这里说一下,是为了让大家对去耦原理认识更深。

方法二:利用目标阻抗计算电容量(设计思想很严谨,要吃透)

为了清楚的说明电容量的计算方法,我们用一个例子。要去耦的电源为 1.2V,容许电压波动为 2.5%, 大瞬态电流 600mA,

步:计算目标阻抗

第二步:确定稳压电源频率响应范围。

和具体使用的电源片子有关,通常在 DC 到几百 kHz 之间。这里设为 DC 到 100kHz。在100kHz 以下时,电源芯片能很好的对瞬态电流做出反应,高于 100kHz 时,表现为很高的阻抗,如果没有外加电容,电源波动将超过允许的 2.5%。为了在高于 100kHz 时仍满足电压波动小于 2.5%要求,应该加多大的电容?

第三步:计算 bulk 电容量

当频率处于电容自谐振点以下时,电容的阻抗可近似表示为:“” 频率 f 越高,阻抗越小,频率越低,阻抗越大。在感兴趣的频率范围内,电容的 大阻抗不能超过目标阻抗,因此使用 100kHz 计算(电容起作用的频率范围的 低频率,对应电容 高阻抗)。

第四步:计算 bulk 电容的 高有效频率

第五步:计算频率高于 1.6MHz 时所需电容

假设使用某公司的 0402 封装陶瓷电容,寄生电感约为 0.4nH,加上安装到电路板上后过孔的寄生电感(本文后面有计算方法)假设为 0.6nH,则总的寄生电感为 1 nH。为了满足总电感不大于 0.16 nH 的要求,我们需要并联的电容个数为:1/0.016=62.5 个,因此需要 63 个 0402 电容。

为了在 1.6MHz 时阻抗小于目标阻抗,需要电容量为:

因此每个电容的电容量为 1.9894/63=0.0316 uF。

综上所述,对于这个系统,我们选择 1 个 31.831 uF 的大电容和 63 个 0.0316 uF 的小电容即可满足要求。

3、相同容值电容并联

使用很多电容并联能有效地减小阻抗。63 个 0.0316 uF 的小电容(每个电容 ESL 为 1 nH)并联的效果相当于一个具有 0.159 nH ESL 的 1.9908 uF 电容。

“图图 10 多个等值电容并联

单个电容及并联电容的阻抗特性如图 10 所示。并联后仍有相同的谐振频率,但是并联电容在每一个频率点上的阻抗都小于单个电容。

但是,从图中我们看到,阻抗曲线呈 V 字型,随着频率偏离谐振点,其阻抗仍然上升的很快。要在很宽的频率范围内满足目标阻抗要求,需要并联大量的同值电容。这不是一种好的方法,造成极大地浪费。有些人喜欢在电路板上放置很多 0.1uF 电容,如果你设计的电路工作频率很高,信号变化很快,那就不要这样做, 好使用不同容值的组合来构成相对平坦的阻抗曲线。

4、不同容值电容的联与反谐振

容值不同的电容具有不同的谐振点。图 11 画出了两个电容阻抗随频率变化的曲线。

“图图 11 两个不同电容的阻抗曲线

左边谐振点之前,两个电容都呈容性,右边谐振点后,两个电容都呈感性。在两个谐振点之间,阻抗曲线交叉,在交叉点处,左边曲线代表的电容呈感性,而右边曲线代表的电容呈容性,此时相当于 LC 并联电路。对于 LC 并联电路来说,当 L 和 C 上的电抗相等时,发生并联谐振。因此,两条曲线的交叉点处会发生并联谐振,这就是反谐振效应,该频率点为反谐振点。

两个容值不同的电容并联后,阻抗曲线所示。从中我们可以得出两个结论:a 不同容值的电容并联,其阻抗特性曲线的底部要比图 10 阻抗曲线的底部平坦得多(虽然存在反谐振点,有一个阻抗尖峰),因而能更有效地在很宽的频率范围内减小阻抗。

b 在反谐振(Anti-Resonance)点处,并联电容的阻抗值无限大,高于两个电容任何一个单独作用时的阻抗。并联谐振或反谐振现象是使用并联去耦方法的不足之处。

在并联电容去耦的电路中,虽然大多数频率值的噪声或信号都能在电源系统中找到低阻抗回流路径,但是对于那些频率值接近反谐振点的,由于电源系统表现出的高阻抗,使得这部分噪声或信号能量无法在电源分配系统中找到回流路径, 终会从 PCB 上发射出去(空气也是一种介质,波阻抗只有几百欧姆),从而在反谐振频率点处产生严重的 EMI 问题。

因此,并联电容去耦的电源分配系统一个重要的问题就是:合理的选择电容,尽可能的压低反谐振点处的阻抗。

ESR 对反谐振(Anti-Resonance)的影响Anti-Resonance 给电源去耦带来麻烦,但幸运的是,实际情况不会像图 12 显示的那么糟糕。

实际电容除了 LC 之外,还存在等效串联电阻 ESR。

因此,反谐振点处的阻抗也不会是无限大的。实际上,可以通过计算得到反谐振点处的阻抗,X 为反谐振点处单个电容的阻抗虚部(均相等)。