模拟 DC-DC 转换器的脉冲频率调制

PFM 降压转换器

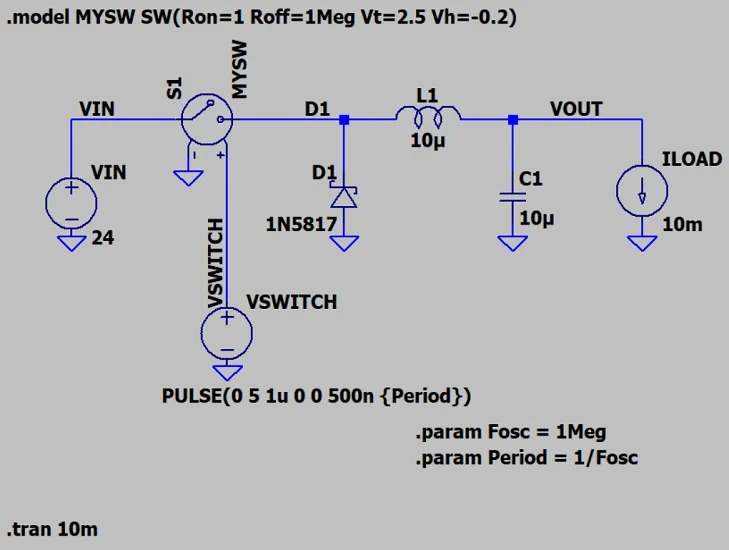

如果您阅读过我的降压转换器仿真指南,您可能会觉得图 1 很熟悉——我们在那篇文章中研究的 PWM 降压转换器与下面的电路具有相同的总体结构。

图 1.在 LTspice 中实现的 PFM 降压转换器。

不过,因为我们使用的是 PFM,所以我对脉冲函数有不同的参数。这是一种固定导通时间 PFM 方案,导通时间为 500 ns,启动周期为 1 μs。

初始设置与 PWM 控制相同,开关频率为 1 MHz(周期为 1 μs),占空比为 50%。不过,如前所述,我们没有使用 PWM,因此当我们开始进行调整时,我们不会修改占空比,同时保持脉冲频率恒定。相反,我们将修改频率。这也会导致占空比发生变化,因为:

占空比

=

准时

周期

并且周期与频率成反比。在此示例中,由于周期会增加,而导通时间固定为 500 ns,因此占空比会减少。

图 2 显示了我们的 PFM 降压转换器的V OUT行为。

显示 PFM 降压转换器输出电压的 LTspice 图。

图 2. 脉冲频率调制降压转换器的输出电压。

只需 10 mA 的负载电流,50% 占空比开关控制波形即可产生不低于输入电压很多的输出电压。为了产生更符合占空比和V IN与V OUT比率之间的理论关系的输出电压值,我们需要显着增加负载电流。

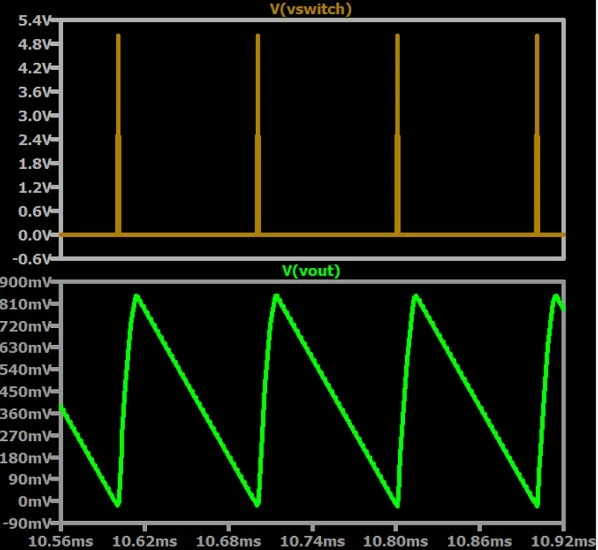

图 3 显示了输出纹波及其与开关动作的关系。

LTspice 图显示了 PFM 降压转换器的开关电压和输出电压。

图 3. PFM 降压转换器的开关电压(顶部)和输出电压(底部)。

降低脉冲频率

PFM 在低负载电流情况下非常有用,因为降低的开关频率意味着更少的转换,从而降低了开关损耗。总体结果是比 PWM 实现的效率更高,无论负载电流如何,PWM 都具有相同的转换数量。

图 4 显示了如果将F OSC参数从 1 MHz 更改为 100 kHz, V OUT会发生什么情况。

开关频率为 100 kHz 时 PFM 降压转换器输出电压的 LTspice 图。

图 4. F OSC = 100 kHz时的 PFM 降压转换器输出电压。

输出电压下降了一点,但总体而言,即使我们将脉冲频率降低了一个数量级,电路仍然工作得很好。同时,较低的开关频率大大减少了开关转换所浪费的能量。

为了帮助演示 PFM 如何在开关稳压器中工作,我将进一步将开关频率降低至 10 kHz,并将负载电流从 10 mA 增加至 100 mA。这些都是巨大的变化 — 您可以在图 5 中看到结果。

LTspice 图显示了 PFM 降压转换器的开关和输出电压。 开关频率等于10kHz; 负载电流等于100 mA。

图 5.PFM降压转换器开关和输出电压。F OSC = 10 kHz, I负载= 100 mA。

事情看起来不再太好了。让我们放大看看发生了什么(图 6)。

图5的放大图。

图 6.图 5 中开关电压和输出电压的放大图。

我觉得这个情节特别说明问题。每个开关脉冲从输入电源汲取能量并将其传输到电路的输出部分,电路需要该能量来提供负载电流。然而,由于脉冲的活动持续时间相对于其非活动持续时间非常短,因此能量在每个周期期间都会被耗尽。因此,转换器无法维持稳定的输出电压。

如果我们将负载电流保持在 100 mA,并将F OSC参数增加回 100 kHz,我们会看到相同的基本行为。不过,现在转换器能够产生约 6V 的稳定输出电压,且纹波幅度在可容忍范围内(图 7)。

PFM 降压转换器的开关和输出电压的 LTspice 图。 开关频率等于 100 kHz,负载电流等于 100 mA。

图 7.PFM 降压转换器开关和输出电压。F OSC = 100 kHz, I负载= 100 mA。

这些图有助于传达 PFM 电压转换的基本操作动态。每个脉冲以电流的形式将能量传输到输出侧。降低这些脉冲的频率可以提高效率,但脉冲仍然必须足够频繁地出现,以满足负载电路的能量需求。

一种用于 PFM 控制的单触发电路

具有非常低脉冲频率的 V SWITCH绘图帮助我们认识到 PFM 与 PWM 不同,不需要连续运行的振荡器,并且 PFM 控制波形实际上并不是典型的振荡器信号。相反,它更像是一系列广泛分离的单次脉冲。如果这些脉冲是由输出条件而不是时钟信号触发的,我们可以通过减少稳压器控制电路消耗的静态电流来进一步提高效率。

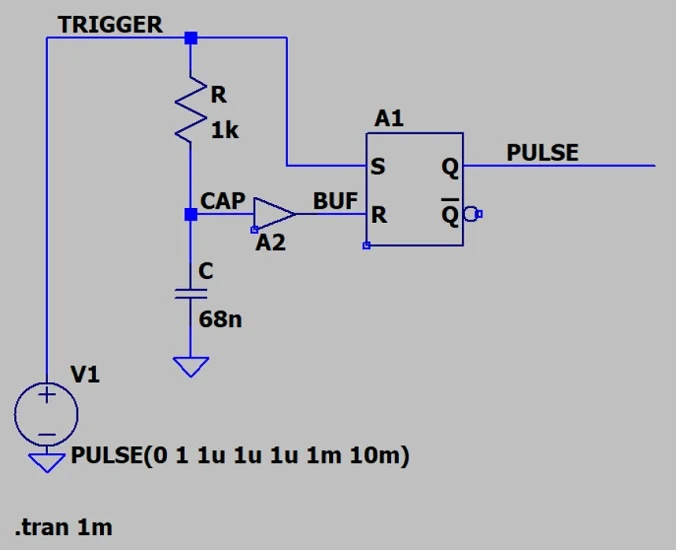

如果您想将一些闭环功能集成到基于 PFM 的稳压器仿真中,脉冲发生器会派上用场。图 8 说明了在 LTspice 中创建触发脉冲发生器的方法。

触发脉冲发生器的 LTspice 原理图。

图 8.在 LTspice 中实现的触发脉冲发生器。

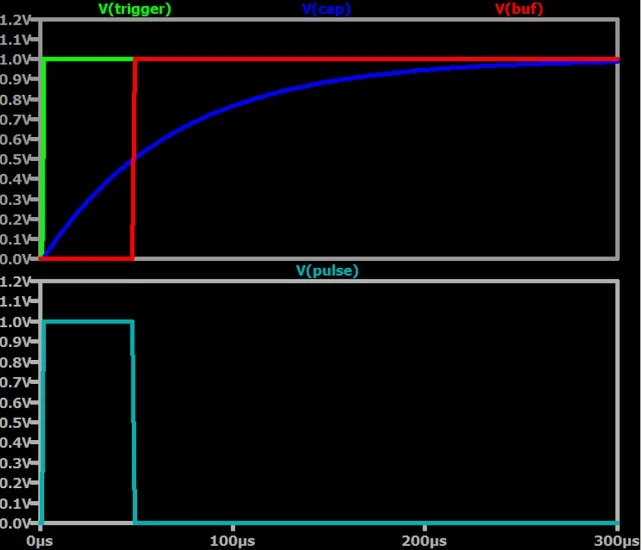

图 9 演示了电路的工作模式。当触发信号(V TRIGGER )变高时, SR锁存器(V PULSE )的输出也变高。触发信号还通过电阻器对电容器(V CAP )充电。当电容器两端的电压达到 0.5V(LTspice 的默认逻辑阈值)时,缓冲器输出 ( V BUF ) 变为逻辑高电平并重置锁存器,将V PULSE驱动回逻辑低状态。

显示触发脉冲发生器操作的 LTspice 图。

图 9.触发脉冲发生器操作。

您可以通过改变电阻器或电容器的值来控制输出脉冲的宽度。请注意,触发信号的逻辑高电平持续时间必须长于脉冲宽度。